Featured post

Top 5 books to refer for a VHDL beginner

VHDL (VHSIC-HDL, Very High-Speed Integrated Circuit Hardware Description Language) is a hardware description language used in electronic des...

Tuesday, 15 June 2021

Top 5 books to refer for a VHDL beginner

Monday, 7 June 2021

Effective VIM Editor tips, tricks and plugins to improve coding speed in VLSI

One of our colleagues always had to struggle with the Verilog / SystemVerilog syntax. Whenever he opens a .sv file he needs to set the syntax manually as ":set syntax=verilog". This really kills time, especially when you are working on a project with tight schedules.

Opening a fine using GVIM

Shortcuts for moving the cursor:

Shortcuts for quick editing:

How do I switch between panes in a split mode in Vim/GVIM ??

How to remove blank lines from a file?

How to implement AUTO-COMPLETION

Tuesday, 4 May 2021

UVM Interview Questions - 6

Q36: What is the Difference between UVM_ALL_ON and UVM_DEFAULT?

UVM_ALL_ON and UVM_DEFAULT are identical. As per the UVM reference manual:UVM_ALL_ON: Set all operations on (default).

UVM_DEFAULT: Use the default flag settings.

Q37: What drain time in UVM?

class test_base extends uvm_test; // ... function void end_of_elaboration_phase(uvm_phase phase); uvm_phase main_phase = phase.find_by_name("main", 0); main_phase.phase_done.set_drain_time(this, 10); endfunction // ... endclass

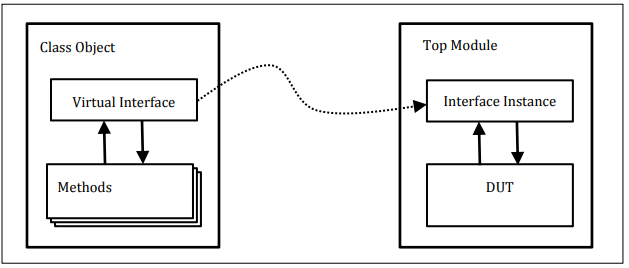

Q38: What is Virtual interface and how Virtual interface is used?

module top;…dut_if dif;…initial beginuvm_config_db#(virtual dut_if)::set(null, "*", "vif", dif);run_test();endendmoduleclass tb_driver extends uvm_driver #(trans1);…virtual dut_if vif;…function void build_phase(uvm_phase phase);super.build_phase(phase);// Get the virtual interface handle that was stored in the// uvm_config_db and assign it to the local vif field.if (!uvm_config_db#(virtual dut_if)::get(this, "", "vif", vif))`uvm_fatal("NOVIF", {"virtual interface must be set for: ",get_full_name(), ".vif"});endfunction…endclass

Q39: How to add a user-defined phase in UVM?

If needed a user can create user-defined phases in the UVM environment. However, this may impact the re-usability of the component. To define a custom phase user need to extend the appropriate base class for phase-type. Following are the available base classes.

class my_phase extends uvm_task_phase;

class my_phase extends uvm_topdown_phase;

class my_phase extends uvm_bottomup_phase;

You can refer to the UVM PHASE IMPLEMENTATION EXAMPLE for complete user-defined phase understanding.

Q40: How interface is passed to components in UVM?

-

This is 8-bit microprocessor with 5 instructions. It is based on 8080 architecture. This architecture called SAP for Simple-As-Possible comp...

-

String data type is used for storing strings, the size is dynamic and string data types come with build in methods. If you have ever tried...

-

Q1: What is UVM? What is the advantage of UVM? Ans: UVM (Universal Verification Methodology) is a standardized methodology for verify...

-

1. 8-bit Micro Processor 2. RISC Processor in VLDH 3. Floating Point Unit 4. LFSR - Random Number Generator 5. Versatile Counter 6. ...

-

This is in continuation of our previous post on Low Power Design Techniques , where we learned about different types of strategies used to...