It is an interesting Architectural decision, what should be our FIFO depth?

when there is a requirement for FIFO? when the Transmitter data rate and the receive data rate are not in sync rather they don't match.

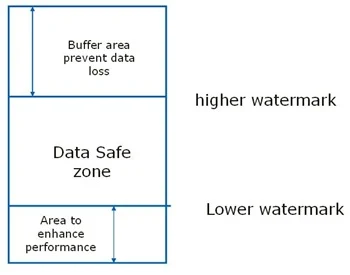

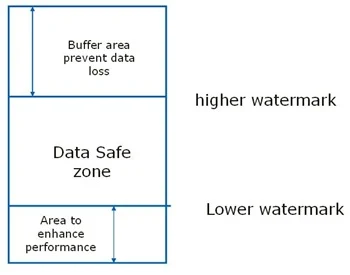

The read is slower than the write, so there is always a chance the data will be lost, so FIFO will be an intermediate logic where the data would be buffered or stored .

smaller FIFO depth can cause overflow scenario and cause a data loss

Possible scenario's:

Scenario 1:

Write is in maximum condition & Read is in minimum condition, means Write process is writing the data faster and read is reading or accessing the data slowest.

Scenario 2:

Whether the design supports only single writes or burst writes also. It becomes more complex when burst writes are present.

Scenario 3:

Write with no idle cycles and read with idle cycles.

Scenario 4:

Is the design requirement is of Synchronous FIFO or an asynchronous FIFO?

Synchronous FIFO: A First In First Out memory, where in the has a control logic mechanism, has read and write pointers, generates Status signals and places handshake signals across. Sync FIFO has a same clock frequency for both read and write operation.

The control/status signals could be Read Error, Write Error signals generated. Read Error generated when the FIFO is empty and Write Error is generated when the FIFO is full, writing may cause a data loss.Based on these signals can generate interrupt signals to act upon. Handshake signals could be Read Enable or a Write Enable, Write Acknowledge and read acknowledge.

Asynchronous FIFO: The operation of Write and Read of a FIFO is purely asynchronous.

Scenario 5:

The Data width of an Tx and Rx are different.