Designers who rely on their iPhones as much as their PCs now have a quick and easy way to determine the power consumption of Xilinx's 28nm 7 series Field Programmable Gate Arrays (FPGA). The new Pocket Power Estimator (PPE) application for Apple's iPhone enables designers to see how Xilinx's 28nm programmable platforms stack up to alternatives in delivering the lowest power consumption for their systems. Designers can download the PPE from the Apple App Store today and, for the first time ever, quickly and easily explore what-if-scenarios and get immediate feedback on the estimated power consumption compared to alternatives. For more complex and detailed power analyses, designers can use the ISE® Design Suite's XPower Estimator (XPE) and the XPower Analyzer (XPA) tools.

"Manufacturers of electronic systems across all our market segments are eager to either lower their current power budgets or drive higher system performance within the same power budgets," said Xilinx Distinguished Engineer and resident power 'guru' Matt Klein. "Offering the Power Pocket Estimator (PPE) on one of the most popular smartphone platforms puts power estimation in the hands of busy designers who routinely turn to their iPhone to access information, further enhancing their design productivity."

The PPE app, which can also be used with the iPad, offers an easy-to-use GUI for the quick entering of resource requirements - such as SerDes utilization, DSP, memory, logic capacity and more. Compared to the previous generation 40nm FPGAs, Xilinx 7 series FPGAs deliver about 50 percent lower total power, on average, thanks in part to the HPL (high-performance/low-power) process technology offered by foundry partner TSMC. Further components of the power envelope that drive this total power reduction include 65 percent lower maximum (worst case) static power, 25 percent lower dynamic power, 30 percent lower I/O power, and 60 percent lower transceiver power. The PPE app takes into account these aspects of total power consumption to enable designers to easily obtain a high-level estimate of power usage by functional block, and how it compares to other Xilinx or competing devices. The PPE also includes application reference examples that designers can use as starting points to customize to their own specifications. The first release of the app includes design examples for the wired and wireless communications markets, while future releases will have additional market segment examples and support other Smartphone platforms.

7 Series Low Power Benefits:

The 28 HPL process technology avoids many yield and leakage issues seen with the embedded SiGe process used in the 28nm HP process and delivers a more cost-effective process solution. The 7 series' larger design headroom, resulting in greater voltage headroom enabled by the HPL process, allows the choice of operating voltages at a wider range of values and enables a flexible power/performance strategy. This enables Xilinx to offer the new low power -2L option for every 7 series device, providing mid-speed-grade performance at 45 percent lower static power compared to the commercial offering. The same -2L device can also function at 0.9V core voltage to provide lower power benefit, including 55 percent lower static power and 20 percent lower dynamic power compared the equivalent commercial speed grade offering.

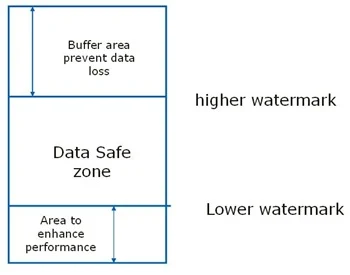

On the design tool side of power optimization, Xilinx introduced the first automated, fine-grained clock-gating solution for FPGAs that can reduce dynamic power by up to 30 percent. This automated capability links to the place and route portion of the standard FPGA design flow and uses a set of innovative algorithms to perform an analysis on all portions of the design to create fine-grain clock-gating or logic-gating signals that neutralize superfluous switching activity. The power benefit of the intelligent clock gating can easily be realized in the PPE app by using the power optimization option. Furthermore, it is important to estimate the power consumption under worst-case conditions. The Xilinx PPE app is designed to provide the estimated total power under max conditions to provide a reasonable and realistic estimate for the respective design scenario.

Availability:

The Xilinx PPE mobile application is free of charge and is available now on the Apple App Store. A version of PPE for Android and other Smartphone platforms will be introduced later this year. To learn more about Xilinx's lower power advantage, view the YouTube video, and link to the PPE App, please visit http://www.xilinx.com/power .

About Xilinx:

Xilinx is the worldwide leader in complete programmable logic solutions. For more information, visit http://www.xilinx.com/.