This is in continuation of our previous post on Low Power Design Techniques, where we learned about different types of strategies used to reduce the power consumption in integrated circuits. Here we will discuss about UPF (Unified Power Format). We will learn the following related to UPF.

What is UPF?

When does it started?

How to use UPF in design?

Who supports it?

The below flow shows the stages of design flow and where UPF is used.

What is UPF?

When does it started?

How to use UPF in design?

Who supports it?

The below flow shows the stages of design flow and where UPF is used.

What is UPF?

The Unified Power Format (UPF). It is intended to ease the job of specifying, simulating, and verifying IC designs that have a number of power states and power islands.

Unified Power Format (UPF) is an industry-wide power format specification to implement low power techniques in a power-aware design flow. UPF is designed to reflect the power intent of a design at a relatively high level. UPF scripts help describe power intent such as:

* Which power rails to be routed to individual blocks.

* When blocks are expected to be powered up or shut down.

* How voltage levels should be shifted between two different power domains.

* And type of measures taken for memory cells and retention registers contents if the primary power supply to a domain is removed.

Hence making the design to be more power-efficient. With power becoming an important factor in today's electronic systems, there is a need for a more systematic approach to reduce the power in complex designs; and UPF is developed to address this need.

When does it started?

A Unified Power Format (UPF) technical committee was formed by the Accellera organization, chaired by Stephen Bailey of Mentor Graphics. As a reaction to the Power Forward Initiative, the group was proposed in July 2006 and met on September 13, 2006.[1] It submitted its first draft in January 2007, and a version 1.0 was approved to be published on February 26, 2007. Joe Daniels was a technical editor.

How to use UPF in design?

Tcl, the tool control language is the backbone of UPF, as well as the similar Common Power Format (CPF), Tcl is a scripting language originally created to provide a way to automate the control of design software.

The attraction of Tcl is that command-line commands can be used as statements in a script. Most Tcl implementations are specific to an individual tool. However, the CPF and UPF definitions are unusual in that they are meant to be used with all tools in a power-aware flow – the tools themselves have to determine whether the commands supplied in the Tcl script are relevant to them or not.

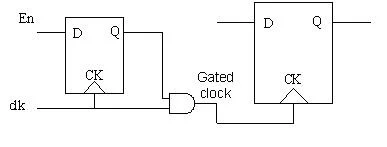

The Tcl command “create_power_domain”, for example, is used by UPF-aware tools to define a set of blocks in the design that are treated as one power domain that is supplied differently to other blocks on the same chip. The idea behind this type of command is that power-aware tools read in the description of which blocks in a design can be powered up and down independently. The tools can use that information to determine, for example, how the simulation will behave under different conditions.

For example, a testbench written in SystemVerilog may identify to the simulator that a particular block should be powered down to ensure that other blocks do not access it without checking on power status first.

A transistor-level simulation may use the power definitions to see what happens when supply voltages or substrate bias voltages change. Do all the necessary logic paths meet expected timing when the supply voltage to one block is lowered to save power while others are running at their maximum voltage? Similarly, a static analysis tool may check that the correct level shifters are in place to determine whether blocks in different power domains can communicate.

Who support it?

A number of EDA vendors have chosen to support UPF in their flows, including Mentor Graphics and Synopsys. However, support is not universal. Cadence Design Systems supports the Common Power Format originally developed by the company but which is now administered by the Silicon Integration Initiative but has declared support for the latest version of IEEE 1801, which incorporates a number of features from CPF.

Let us know in the comments if you wish to know about any specific details regarding UPF.