Q36: What is the Difference between UVM_ALL_ON and UVM_DEFAULT?

UVM_ALL_ON and UVM_DEFAULT are identical. As per the UVM reference manual:UVM_ALL_ON: Set all operations on (default).

UVM_DEFAULT: Use the default flag settings.

Q37: What drain time in UVM?

class test_base extends uvm_test; // ... function void end_of_elaboration_phase(uvm_phase phase); uvm_phase main_phase = phase.find_by_name("main", 0); main_phase.phase_done.set_drain_time(this, 10); endfunction // ... endclass

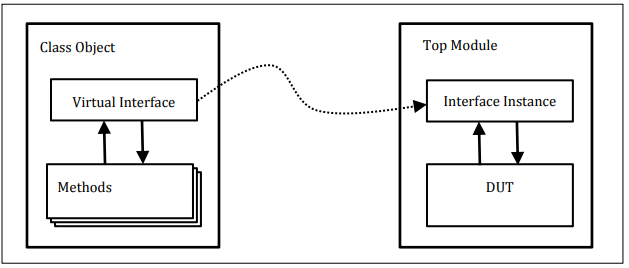

Q38: What is Virtual interface and how Virtual interface is used?

module top;…dut_if dif;…initial beginuvm_config_db#(virtual dut_if)::set(null, "*", "vif", dif);run_test();endendmoduleclass tb_driver extends uvm_driver #(trans1);…virtual dut_if vif;…function void build_phase(uvm_phase phase);super.build_phase(phase);// Get the virtual interface handle that was stored in the// uvm_config_db and assign it to the local vif field.if (!uvm_config_db#(virtual dut_if)::get(this, "", "vif", vif))`uvm_fatal("NOVIF", {"virtual interface must be set for: ",get_full_name(), ".vif"});endfunction…endclass

Q39: How to add a user-defined phase in UVM?

If needed a user can create user-defined phases in the UVM environment. However, this may impact the re-usability of the component. To define a custom phase user need to extend the appropriate base class for phase-type. Following are the available base classes.

class my_phase extends uvm_task_phase;

class my_phase extends uvm_topdown_phase;

class my_phase extends uvm_bottomup_phase;

You can refer to the UVM PHASE IMPLEMENTATION EXAMPLE for complete user-defined phase understanding.