Researchers around the world have looked for ways to take full advantage of its many desirable properties. Now scientists have discovered a material that has a similar electronic structure to graphene but can exist in three dimensions, instead of a flat sheet like graphene, could lead to faster transistors and more compact hard drives.

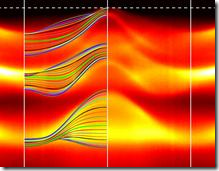

Plot of energy levels of electrons in trisodium bismuthide showing that this bulk material has properties similar to graphene.

The material is called three-dimensional topological Dirac semi-metal (3DTDS) and is a form of the chemical compound sodium bismuthate, Na3Bi.

Researchers led by scientists from Oxford University, Diamond Light Source, Rutherford Appleton Laboratory, Stanford University, and Berkeley Lab's Advanced Light Source, has discovered 3DTDS.

'The 3DTDS we have found has a lot in common with graphene and is likely to be as good or even better in terms of electron mobility – a measure of both how fast and how efficiently an electron can move through a material,' said Dr Yulin Chen of Oxford University's Department of Physics.

'You can think of the electronic structure of the 3DTDS as being rather like that of the graphene – the so called ''Dirac cone'' where electrons collectively act as if they forget their mass – but instead of flowing masslessly within a single sheet of atoms, the electrons in a 3DTDS flow masslessly along all directions in the bulk.'

Moreover, unlike in graphene, electrons on the surface of the 3DTDS remember their 'spin' – a quantum property akin to the orientation of a tiny magnet that can be used to store and read data – so that the magnet information can be directly transferred by the electric current, which could enable faster and more efficient spintronic devices.

'An important property of this new type of material is its magnetoresistance – how its electrical resistance changes when a magnetic field is applied,' said Dr Chen. 'In typical Giant Magnetoresistance Materials (GMR) the resistance changes by a few tens of percent and then saturate but with 3DTDS it changes 100s or 1000s of percent without showing saturation with the external magnetic field. With this much larger effect we could make a hard drive that is higher intensity, higher speed, and lower energy consumption – for example turning a 1 terabyte hard drive into a drive that can store 10 terabytes within the same volume.'

While this particular compound is too unstable to use in devices, the team is testing more stable compounds and looking for ways to tailor them for applications.

Dr Chen said: 'Now that we have proved that this kind of material exists, and that such compounds can have one of the highest electron mobilities of any material so far discovered, the race is on to find more such materials and their applications, as well as other materials with unusual topology in their electronic structure.'