We have learned and use the decimal numbering system simply because humans are born with ten fingers! Hence, the numeric system we is the decimal number system, but this system is not convenient for machines since the information is handled codified in the shape of ON or OFF bits.

This means, we have to learn the binary system in addition to the decimal system. We also will discuss the octal and hexadecimal systems because conversion to/from binary is easy and numbers in these systems are easier to read than binary numbers for humans.

This way of codifying takes us to the necessity of knowing the positional methods of calculation which will allow us to express a number in any base where we need it.

A base of a number system or radix defines the range of values that a digit may have.

Binary Number System

In the binary system or base 2, there can be only two values for each digit of a number, either a "0" or a "1".

Digital and computer technology is based on the binary number system, since the foundation is

based on a transistor, which only has two states: on or off.

Each digit of the number is called a bit or which is a short for binary digits.

- An 8-bit group is referred to as a Byte

- An 4-bit group is referred to as a nibble

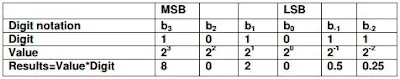

Each bit is weighted based on its position in the sequence (powers of 2) from the Least

Significant Bit (LSB) to the Most Significant Bit (MSB).

Each bit must be less than 2 which means it has to be either 0 or 1.

For example (1010.11)2 is evaluated as:

(1010.11)2 = 8 + 0 + 2 + 0 + 0.5 + 0.25 = (10.75)10

Note: The general term for decimal point is radix point

In binary, the count starts at 0 (called 0-referencing), where in decimal, the count typically starts

with 1 (called 1-referencing)

Octal Number System

In the octal system or base 8, there can be eight choices for each digit of a number:

"0", "1", "2", "3", "4", "5", "6", "7".

Octal number systems are used by humans as a representation of long strings of bits since they are:

- Easier to read and write, for example 347 in octal is easier to read and write than 011100111 in binary.

- Easy to convert (Groups of 3 or 4)

- The most common way is to use Hex to write the binary equivalent; two hexadecimal digits make a Byte (groups of 8-bit), which are basic blocks of data in Computers.

Decimal Number System

In the decimal system or base 10, there are ten different values for each digit of a number:

"0", "1", "2", "3", "4", "5", "6", "7", "8", "9".

Decimal number system is default and easy to use for us. For example when you see a number 56 your assumption is that its base or radix is 10 i.e. “56 base 10”.

- Each digit is weighted based on its position in the sequence (power of 10) from the Least

Significant Digit (LSD, power of 0) to the Most Significant Digit (MSD, highest power).

- Each digit must be less than 10 (0 to 9)

Hexadecimal Number System

In the hexadecimal system, we allow 16 values for each digit of a number:

"0", "1", "2", "3", "4", "5", "6", "7", "8", "9", "A", "B", "C", "D", "E", and "F".

Where “A” stands for 10, “B” for 11 and so on.

Conversion among different radices

1. Convert from Decimal to Any Base

Let’s think about what you do to obtain each digit. As an example, let's start with a decimal number 1234 and convert it to decimal notation. To extract the last digit, you move the decimal point left by one digit, which means that you divide the given number by its base 10.

1234/10 = 123 + 4/10

The remainder of 4 is the last digit. To extract the next last digit, you again move the decimal point left by one digit and see what drops out.

123/10 = 12 + 3/10

The remainder of 3 is the next last digit. You repeat this process until there is nothing left. Then you stop. In summary, you do the following:

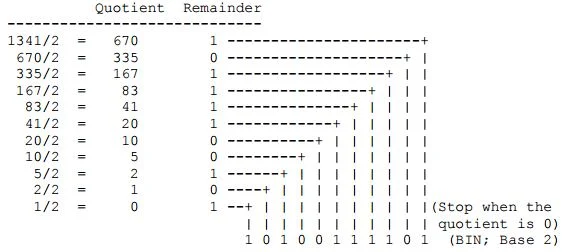

Conversion of decimal number to binary

Now, let's try a nontrivial example. Let's express a decimal number 1341 in binary notation.

Note that the desired base is 2, so we repeatedly divide the given decimal number by 2.

Conversion of decimal number to octal

Now, let's express the same decimal number 1341 in octal notation.

Conversion of decimal number to hexadecimal

Let's express the same decimal number 1341 in hexadecimal notation.

The easiest way to convert fixed point numbers to any base is to convert each part separately. We begin by separating the number into its integer and fractional part. The integer part is converted using the remainder method, by using a successive division of the number by the base until a zero is obtained. At each division, the reminder is kept and then the new number in the base r is obtained by reading the remainder from the lat remainder upwards.

The conversion of the fractional part can be obtained by successively multiplying the fraction with the base. If we iterate this process on the remaining fraction, then we will obtain successive significant digit. This methods form the basis of the multiplication methods of converting fractions between bases.

Example:

Convert the decimal number 3315 to hexadecimal notation. What about the hexadecimal equivalent of the decimal number 3315.3?

Solution:

Conversion of Any Base to Decimal

Let's try to understand what a decimal number means. For example, 1234 means that there are four boxes (digits); and there are 4 one's in the right-most box (least significant digit), 3 ten's in the next box, 2 hundred's in the next box, and finally 1 thousand's in the left-most box (most significant digit). The total is 1234:

or simply, 1*1000 + 2*100 + 3*10 + 4*1 = 1234

Thus, each digit has a value: 10^0

=1 for the least significant digit, increasing to 10^1

=10, 10^2

=100, 10^3

=1000, and so

forth.

Likewise, the least significant digit in a hexadecimal number has a value of

16^0 =1 for the least significant digit, increasing to

16^1 =16 for the next digit,

16^2 =256 for the next,

16^3 =4096 for the next, and so forth.

Thus, 1234 means that there are four boxes (digits); and there are 4 one's in the right-most box (least significant digit), 3 sixteen's in the next box, 2 256's in the next, and 1 4096's in the left-most box (most significant digit). The total is:

1*4096 + 2*256 + 3*16 + 4*1 = 4660

In summary, the conversion from any base to base 10 can be obtained from the formulae

Where b is the base, di the digit at position i, m the number of digit after the decimal point, n the number of digits of the integer part and X10 is the obtained number in decimal. This form the basic of the polynomial method of converting numbers from any base to decimal

Example: Convert 234.14 expressed in an octal notation to decimal.

Example: Convert the hexadecimal number 4B3 to decimal notation. What about the decimal equivalent of the hexadecimal number 4B3.3?

Example: Convert 234.14 expressed in an octal notation to decimal.