The multi-year deal sees ARM tie itself even closer to TSMC, its chip-fabber of choice, as it looks to capitalise on the company's technology to help it maintain a lead over Intel for chip power efficiency.

ARM is ramping up its push to get its highly efficient low-power chips into servers by signing a multi-year agreement with Asian silicon manufacturer TSMC.

ARM is ramping up its push to get its highly efficient low-power chips into servers by signing a multi-year agreement with Asian silicon manufacturer TSMC.

Under the deal, the Cambridge-based chip designer has agreed to share technical details with TSMC to help the fabricator make better chips with higher yields, ARM said on Monday. TSMC will also share information, so that ARM can create designs better suited to its manufacturing.

"By working closely with TSMC, we are able to leverage TSMC's ability to quickly ramp volume production of highly integrated SoCs [System-on-a-Chip processors] in advanced silicon process technology," Simon Segars, general manager for ARM's processor and physical IP divisions, said in a statement.

"The ongoing deep collaboration with TSMC provides customers earlier access to FinFET technology to bring high-performance, power-efficient products to market," he added.

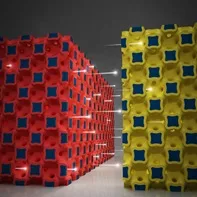

The move should keep ARM's chip designs competitive with Intel's in the server market. TSMC's FinFET is akin to Intel's 3D 'tri-gate' method of designing processors with greater densities, which should deliver greater power efficiency and better performance from a cost point of view.

By tweaking its chips to TSMC's process, ARM chips should deliver good yields on the silicon, keeping prices low while maintaining the higher power efficiency that comes with a lower process node.

ARM's chips dominate the mobile device market, but unlike Intel, it doesn't have a brand presence on the end devices. Instead, companies license its designs, go to a manufacturer, and rebrand the chips under their own name. You may not have heard of ARM, but the Apple, Qualcomm and Nvidia chips in mobile devices, as well as Calxeda and Marvell's server chips, are all based to some degree on based on ARM's low-power RISC-architecture processors.

64-bit processors

As part of the new deal, ARM is expecting to work with TSMC on 64-bit processors. It stressed how the 20nm process nodes provided by the fabber will make its server-targeted chips more efficient, potentially cutting datacentre electricity bills.

"This collaboration brings two industry leaders together earlier than ever before to optimise our FinFET process with ARM's 64-bit processors and physical IP," Cliff Hou, vice president of research and development for TSMC, said in the statement. "We can successfully achieve targets for high speed, low voltage and low leakage."

"We can successfully achieve targets for high speed, low voltage and low leakage" — Cliff Hou, TSMC

However, ARM only released its 64-bit chips in October, putting these at least a year and a half away from production, as licensees tweak designs to fit their devices. Right now, there are few ARM-based efforts pitched at the enterprise, aside from HP's Redstone Server Development platform and a try-before-you-buy ARM-based cloud for the OpenStack software.

Production processes

AMD, like ARM, does not operate its own chip fabrication facilities and so must depend on the facilities of others. AMD uses GlobalFoundries, while ARM licensees have tended to use TSMC. However, both TSMC and GlobalFoundries are a bit behind Intel in terms of the level of detail — the process node — they can make their chips to.

Right now, TSMC is still qualifying its 20nm process for certification by suppliers, while Intel has been shipping its 22nm Ivy Bridge processors for several months. Intel has claimed a product roadmap down to 14nm via use of its tri-gate 3D transistor technology, while TSMC is only saying in the ARM statement it will go beyond 20nm, without giving specifics.

Even with this partnership, Intel looks set to maintain its lead in advanced silicon manufacturing.

"By the time TSMC gets FinFET into production - earliest 2014, it's only just ramping 28nm [now] - Intel will be will into its 2nd generation FinFET buildout," Malcolm Penn, chief executive of semiconductor analysts Future Horizons, told ZDNet. This puts Intel "at least three years ahead of TSMC. Global Foundries will be even later."

Intel has noticed ARM's rise and has begun producing its own low-power server chips under the Centerton codename. However, these chips consume 6W compared with ARM's 5W.

At the time of writing, neither ARM nor TSMC had responded to requests for further information. Financial terms, if any, were not disclosed.